반가산기 논리회로는 두개의 입력을 받아 합(sum)과 올림(carry)를 구하는 조합회로이다.

반가산기의 회로도는 다음과 같이 구성되어 있으며 진리표는 아래와 같다.

반가산기를 Verilog로 설계할 수 있는 툴인 Vivado로 3가지의 HDL 방식을 이용하여 설계 해보았다.

1. 논리 게이트 프리미티브(primitive gate)를 이용한 모델링

2. 연속 할당문을 이용한 모델링

3. 행위수준 모델링

1. 게이트 수준 모델링

Verilog 파일을 half-adder.v 파일과 half-adder-testbench.v를 만든다.

게이트 수준 모델링은 xor와 nand, not게이트로 설계를 하였다. wire c_out_bar는 nand의 출력부분에서 나오는 값으로 not 게이트의 입력값으로 들어간다.

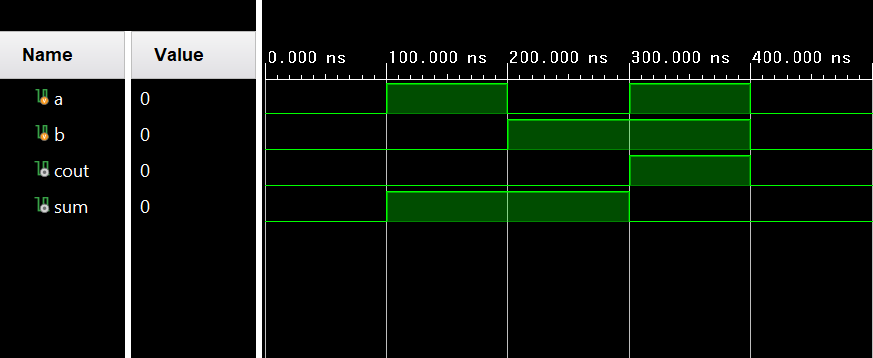

testbench에서 reg를 나타내는 자료형은 입력값을 주기 위해 설정하는 자료형이다. reg a,b로 선언하면 initial begin 사이에서 a,b의 값을 바꿔주며 반가산기의 동작을 확인할 수 있다.

half_adder U0_half_adder(a,b,sum,cout)는 half-adder.v에서 정의한 모듈인 half-adder를 불러와 U0로 선언한 것을 의미한다.

timescale은 10ns/1ps로 맞춰준다.

2. 연속 할당문을 이용한 모델링

assign으로 오른쪽의 연산 결과를 왼쪽의 변수에 넣어주는 모델링 방법이다. assign의 쓰임은 mov명령어와 비슷하다고 생각하면 된다.

sum=a^b; //^연산자는 xor을 의미한다.

cout=a&b;//&연산자는 and를 의미한다.

testbench는 동일하게 작성한다.

3. 행위 수준 모델링

행위 수준 모델링은 복잡한 회로를 설계하기에 적합한 모델링 방법이다. 행위 수준 모델링은 always와 initial 구문 그리고 함수와 task등이 사용된다. always의 조건에는 입력값이 모두 들어가야한다. 하나라도 생략이 되면 결과값이 다르게 나오기 때문이다. 입력값이 많을때는 always @*로 해서 *이 모든 이력값을 대체할 수 있다.

반가산기를 행위수준 모델링을 이용하여 설계하였다.

reg sum, cout은 always 구문안에서 값이 정해지기 때문에 reg로 선언 해줘야한다.

시뮬레이션 결과도 동일하게 나온다.

HDL는 3가지의 방식이 있다. 어느 것이 좋다고 할 순 없지만 아직까진 3개의 차이가 미미하다. 연습을 위해선 지금부터 행위 수준 모델링으로 다음 회로를 설계하도록 하겠다.

'디지털논리회로' 카테고리의 다른 글

| [Verilog] 8bit 가산기 (0) | 2020.03.27 |

|---|---|

| [Verilog] 전가산기 (0) | 2020.03.26 |

| [Verilog] 멀티플렉서 (0) | 2020.03.26 |

| 순차논리회로 (0) | 2020.01.08 |

| 조합논리회로 (0) | 2020.01.08 |