이번에는 1bit의 덧셈이 아닌 8bit를 더해주는 회로인 8bit 가산기를 설계 해보겠다.

8비트 가산기는 다음 그림과 같이 8개의 전가산기로 이루어져있다. 즉 1bit 덧셈을 해주는 전가산기에서 나온 carry 신호가 다음 전가산기로 넘어가서 입력값으로 들어가는 기능을 한다. 여기서 중요한것은 처음 carry0는 0이 된다.

이번 8bit 가산기 또한 전가산기의 모듈을 이용하여 설계할 것이다.

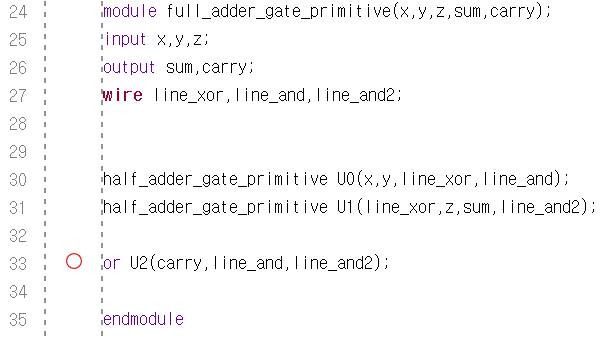

다음은 전가산기 모듈이다.

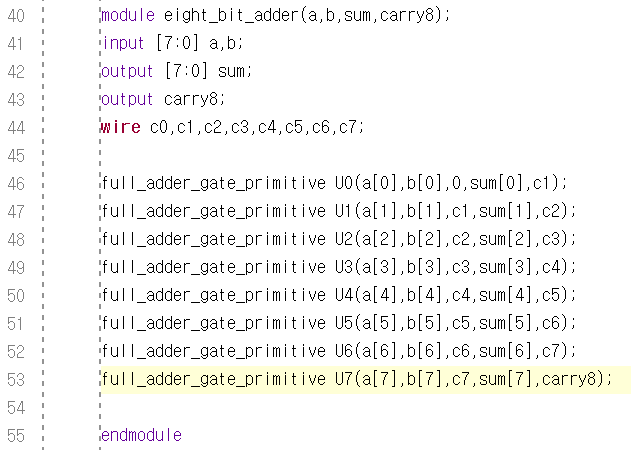

8bit 전가산기를 설계 할 때 입력 변수도 8bit로 설계 해야한다.

verilog에서 1bit이상의 bit를 표현할 때는 '[a:0] variation' 으로 선언한다 이때 variation은 a+1의 비트를 갖는다.

variation[0]은 a+1비트중 첫번째 비트를 표현하고 variation[a]은 a+1번째 비트를 의미한다.

따라서 8bit 가산기에서 두 입력 비트가 각각의 비트 번째에 맞는 비트끼리 덧셈을 해야한다.

(a[0]+b[0], a[1]+b[1]...)

다음 코드와 같이 인풋값인 a,b를 8비트로 선언하고 덧셈의 결과인 sum또한 8비트로 받았다.

각각의 전가산기에서 나오는 carry의 값은 wire로 선언하여 다음 가산기의 인풋값으로 들어가게 선언 하였다.

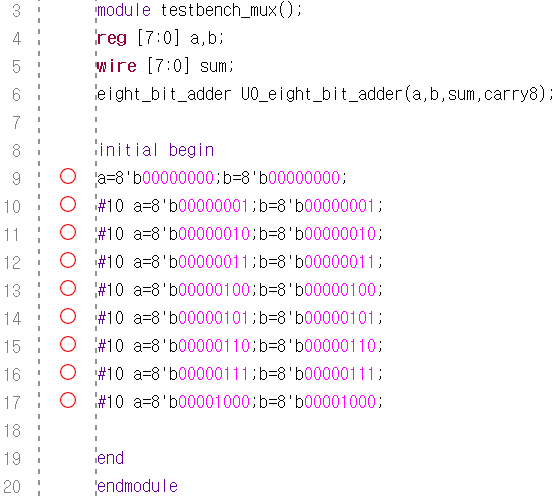

testbench도 wire [7:0]으로 sum의 값을 선언해야 시뮬레이션 결과값에 나온다.

또한 reg 로 선언된 인풋값 a,b도 [7:0]으로 8bit 형태로 선언해야 bus의 형태로 시뮬레이션 결과가 나온다.

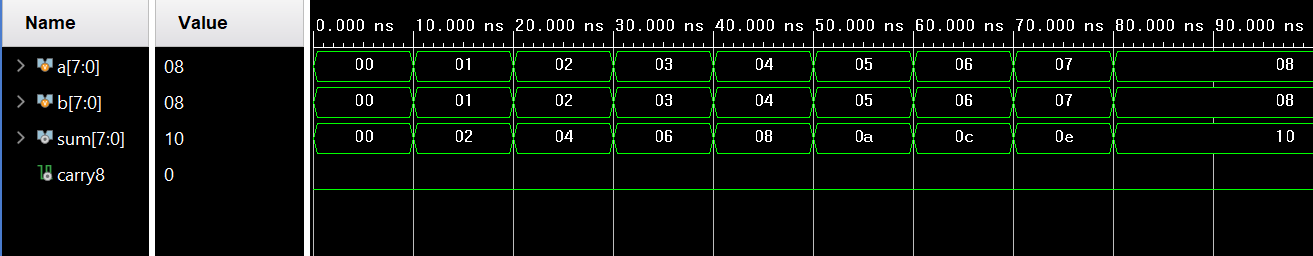

시뮬레이션 결과값이 제대로 출력된다.

결과값에 보이는 것처럼 1bit 이상이 표현되는 것을 bus 형태라고 한다.

'디지털논리회로' 카테고리의 다른 글

| [Verilog] D flipflop (0) | 2020.03.27 |

|---|---|

| [Verilog] JK flipflop (0) | 2020.03.27 |

| [Verilog] 전가산기 (0) | 2020.03.26 |

| [Verilog] 멀티플렉서 (0) | 2020.03.26 |

| [Verilog] 반가산기 (0) | 2020.01.08 |