이번에 설계 할 회로는 조합회로가 아닌 순차회로의 기본이 되는 flipflop 설계를 할 것이다.

flipflop은 정보를 저장하는 기능을 하여 cpu에서 데이터값을 저장하는 레지스터가 flipflop으로 이루어져 있다.

flipflop의 기본적인 특징은 clock pulse의 edge에서만 저장된 데이터가 변하기 때문에 clock pulse가 1일때나 0일때는 값이 변하지 않고 원래 갖고 있던 값을 그대로 갖고 있는다.

clock pulse의 edge는 다음 그림과 같이 1->0으로 되는 부분을 negative edge라 부르고 0->1인 부분을 positive edge라고 부른다.

이번 설계 에서는 positive edge부분에서 데이터 값을 저장하는 jk flipflop을 설계 해보겠다.

jk flipflop은 순차회로이므로 상태표를 만들어야 한다.

다음 그림과 같이 flipflop의 형태를 그릴 수 있다.

Q에 데이터 값이 저장 되어 있다면 J 값과 K값에 의해 Q의 값이 바뀔 것이다.

다음은 JK flipflop의 상태표이다. 원래 순차회로는 상태표를 보면서 verilog 설계를 해야 하지만 JK flipflop은 상태표만 보고 행위 수준 모델링을 하기에는 애매한 부분이 있다.

JK flipflop만 좀 더 세부적으로 Q의 상태 변화를 하나하나 그려 가면서 verilog 행위 수준 모델링을 했다.

J,K의 값에 따라 변하는 Q의 값을 하나하나 그려 가면서 설계를 하였다.

always @() 구문을 이용하여 설계를 해야한다. 여기서 주의 할 점은 reg로 선언한 변수에 값을 넣을려면

always @()구문 안에 넣거나 initial begin end 구문안에 넣어 줘야 한다.

이와 관련된 내용은 추후에 정리할 memory 설계시 자세히 정리 해보겠다.

행위 수준 모델로 설계한 JK flipflop

행위 수준 모델링은 if 문으로 조건문을 사용하여 인풋값에 따른 결과값을 나타내는 방법으로 세가지 방법중 가장 추상적인 방법이다.

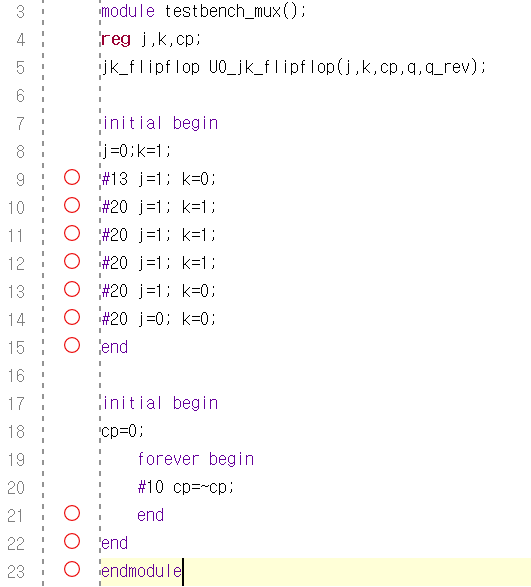

JK flipflop의 testbench 모습

여기서 clk을 생성할 수 있는 코드를 작성한다.

initial begin

cp=0;

forever begin

#10 cp=~cp;

end

end

다음 initial begin문은 cp값을 0과1을 10ns 간격으로 바꿔주는 코드다.

clk값에 맞게 0과1을 계속 해서 바꿔줄 수 있다.

시뮬레이션 결과값

여기서 q와 q_rev값이 초반에 x라고 알 수 없음이 나오는데 여기서 reset 신호를 추가하면 q의 초기값을 지정해 줄 수 있다.

'디지털논리회로' 카테고리의 다른 글

| [Verilog] 인코더, 디코더 (0) | 2020.04.07 |

|---|---|

| [Verilog] D flipflop (0) | 2020.03.27 |

| [Verilog] 8bit 가산기 (0) | 2020.03.27 |

| [Verilog] 전가산기 (0) | 2020.03.26 |

| [Verilog] 멀티플렉서 (0) | 2020.03.26 |